#### Enabling Small Form Factor, Anti-Tamper, High-Reliability, Fan-less Artificial Intelligence and Machine Learning

A Leading Provider of Smart, Connected and Secure Embedded Control Solutions

# **Smart Embedded Vision Today**

Accelerate Smart Embedded Vision at the Edge Supporting 4K Resolutions with Low-Power 12.7 Gbps SERDES

#### Different application use cases with common requirements

- More pixels

- Small form factor

- More secure

1080p moving towards 4K/8K

Not enough space to fit a heat sink and thermal fan

Ensure safe operation and protection against tamper

# **Our Objective Today**

#### Low-power, Fan-less, Artificial Intelligence (AI) Camera for the Edge

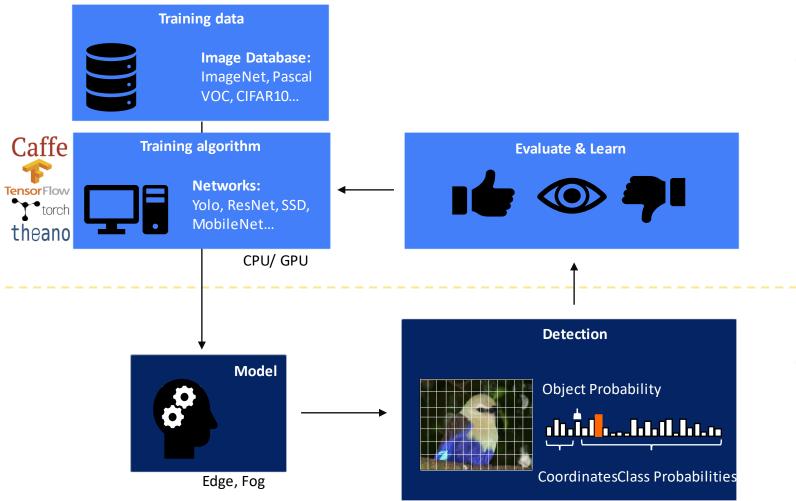

# **The Deep Learning Construct**

#### **Network Training**

- In the data centre or workstation

- Large compute capacity

- No power or space constraints

#### **Inference**

- Need low latency

- Power and space constrained

- Requires security and reliability

© 2021 Microchip Technology Inc. and its subsidiaries

# **Design Challenges – Power**

#### Implications to high power consumption

- Increased module size to fit heat sinks and cooling fans

- Increased BOM

- Increased image processing complexity to manage interference in thermal imaging

- Decreased battery life, increased weight due to larger batteries

- Decreased compute envelope to operate within temperature constraints

Heat sinks needed power consumption > 5W

Active cooling requires fans and onboard power electronics and add up to \$10 in bill of materials (BOM)

Portable, battery-powered devices consuming more power will require heavier batteries

# Design Challenge – Advance Driver Assistance Systems (ADAS)

#### • Implications to safe and reliable operation

- Can the design withstand, detect, correct or report errors arising out of

- Processes, random events and transient causes

- Whether it enables safe designs as prescribed to operate in

- Industrial applications IEC61508

- Automotive applications ISO26262

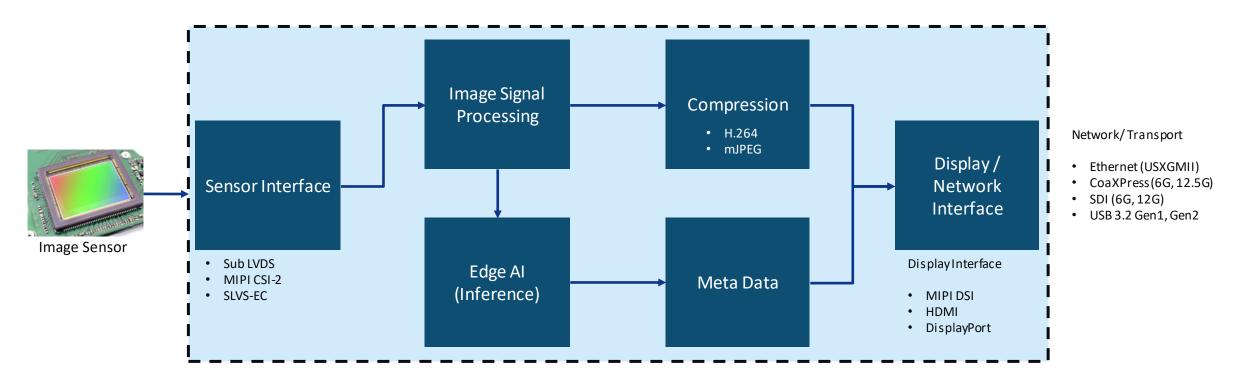

# **Design Challenge – Evolving Requirements**

- Requirements for Embedded Vision

- Newer AI algorithms, more frameworks

- Different sensor interfaces, In-System Programming (ISP), compression techniques, network interfaces

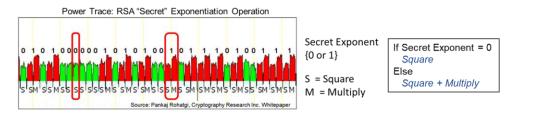

# **Design Challenge – Security**

- Cyber Security is the #1 concern for connected devices on the network edge

- \$400 of DPA hacking equipment can lead to millions of dollars in IP theft

- Side channel attacks to extract secret keys from cryptographic devices

- Simple Power Analysis (SPA) involves visual interpretation of power traces

- Differential Power Analysis (DPA) uses statistical analysis and error correction techniques

- Implications to Security

- Secure storage of weights for a neural network

- Ensure system processors execute authenticated code

- Over the air upgrades for remote installations

- Ensure new devices cannot be programmed with extracted code

- Overbuilding or cloning

# **Design Challenge – Reliability**

- Volumes and deployment locations demand reliability

- Single Event Upsets (SEU) due to Soft-Errors

- Caused due to high-energy particle strikes

- Prevalent in Space and Avionics levels

- Also, at the ground level

- Neutrons generated in Earth's atmosphere

- Alpha particles generated by radioactive isotopes in package materials

- Implications due to SEU lead to catastrophic system failure

- SEU on a data bit in flip-flop can introduce logic errors

- Corrupt bit in data memory may be read multiple times

- Configuration error in programmable logic changes functionality

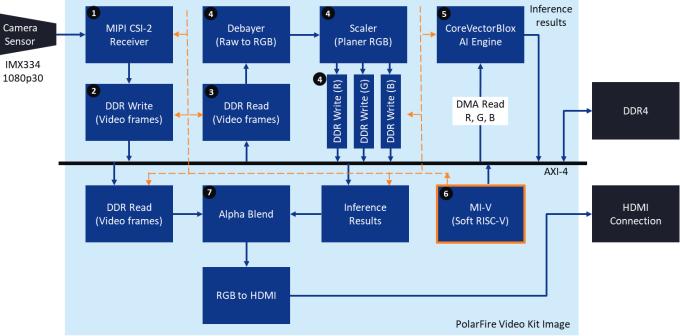

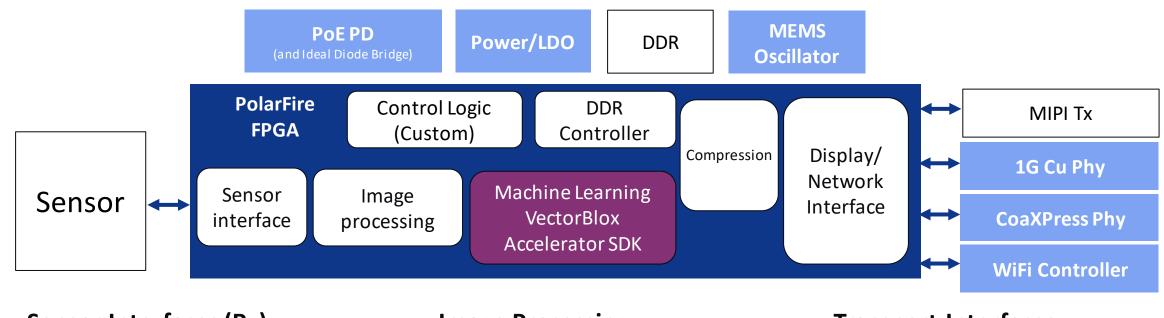

# **Using FPGAs for AI and Embedded Vision**

#### • Sensor Interfaces (Rx)

- MIPI CSI-2

- SLVS-EC v1.2 & v2.0

#### Compression

- H.264 encode

- mJPEG

#### • Image Processing

- Alpha blending

- Bayer interpolation

- Image edge detection

- Image sharpen

- RGB to YCbCr

- YCbCrto RGB

- Histogram

- White balance

- Gamma correction

- $\odot$  2021 Microchip Technology Inc. and its subsidiaries

- Transport Interfaces

- CoaXPress<sup>®</sup> 12G

- SDI 12G

- 10G MAC / 10G PHY

- USXGMII 1, 2.5, 5, 10G

- HDMI 2.0

- DisplayPort 1.4a

- USB 2.0, USB 3.2 Gen1/2

- 10 GigE Vision

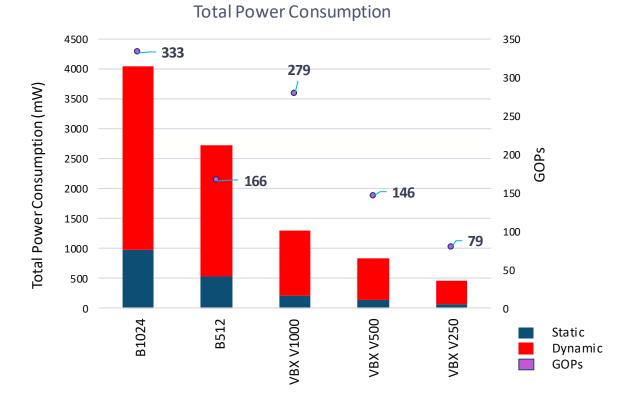

# **Microchip FPGAs Deliver Fan-less Edge Compute**

| Core Name           | Peak GOPs | Dynamic<br>Power<br>(mW) | Static<br>Power*<br>(mW) | Total<br>Power<br>(mW) | Total<br>Power<br>(mW/GOP) |

|---------------------|-----------|--------------------------|--------------------------|------------------------|----------------------------|

| VectorBlox<br>V1000 | 279       | 1094                     | 206                      | 1300                   | 5.1                        |

| VectorBlox<br>V500  | 146       | 698                      | 127                      | 825                    | 6.4                        |

| VectorBlox<br>V250  | 79        | 387                      | 65                       | 452                    | 7.1                        |

| Comp A<br>B1024     | 332.8     | 3072                     | 976                      | 4048                   | 12.2                       |

| Comp A<br>B512      | 166.4     | 2201                     | 528                      | 2729                   | 16.4                       |

- 2-3x more power efficient inferencing for similar performance output

- Suitable for applications requiring

- Low power consumption, small enclosures and fan less designs

\*Scaled for resource utilization

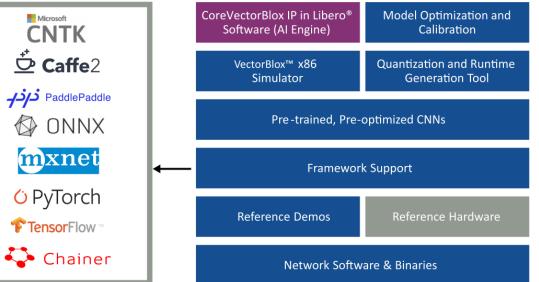

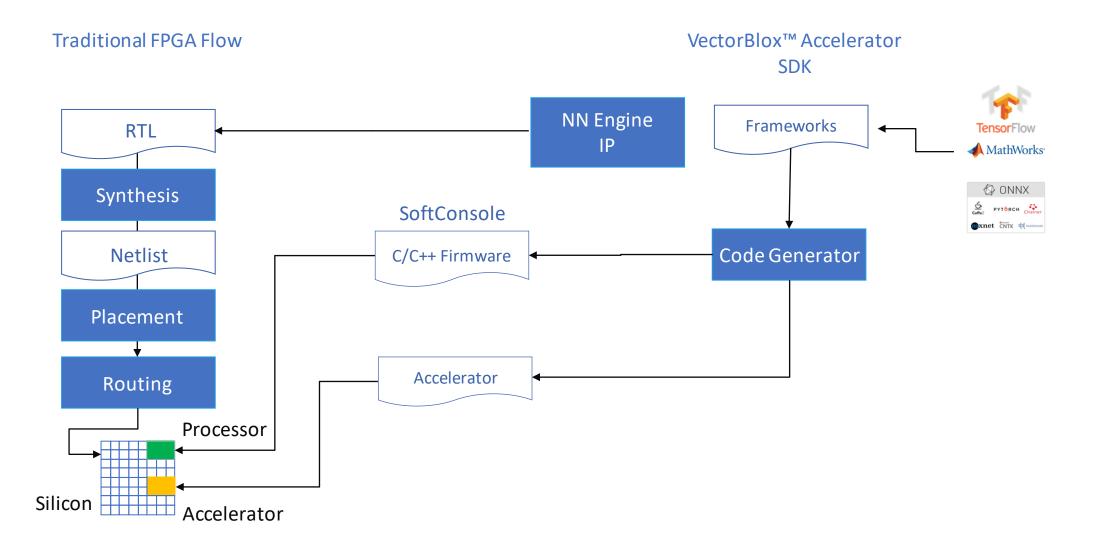

# VectorBlox<sup>™</sup> Software Development Kit (SDK) for Microchip FPGAs

- Enables developers to code in C/C++ and use power-efficient neural networks for inference

- No prior FPGA design experience required

- Accepts models in TensorFlow, ONNX, etc.

- Offers the widest framework interoperability

- Includes a bit accurate simulator

- Validate CNN in software environment

- Pre-trained neural networks demos included

- Load network models at run time on supported hardware

Libero

## **Software Abstraction for Neural Networks**

## **Power Estimation Example: Facial Recognition**

A two-step process, 2 Convolutional Neural Networks (CNN) with one Accelerator

## • First BlazeFace

- Used in mobile apps

- 3.8GOPs with 6M parameters (estimated)

- Multi outputs

- Bounding box

- Eyes, nose, mouth, ears

- Confidence value

### Second SphereFace

- 3.5GOPs with 22M parameters

- Runs on each face detected by BlazeFace

- Input 112x96 image (produced from BlazeFace bounding box)

- Output is a 512 element vector

- 512 vectors are compared to the vector of known faces

- Person of interest photo is run through SphereFace to build a known face vector

# **Power Analysis**

#### Design includes

- V250

- Mi-V (AXI4)

- LSRAM

- AXI4 interconnect

- SPI controller

- Image scaler

- DDR4 controller

| Settings     |             |  |

|--------------|-------------|--|

| General      |             |  |

| Family       | PolarFire   |  |

| Device       | MPF100TS    |  |

| Package      | FCSG325     |  |

| Range        | Extended    |  |

| Core Voltage | 1.0 V       |  |

| Process      | Typical     |  |

| Speed Grade  | -1          |  |

| Data State   | Preliminary |  |

| Thermal Inputs                                                 |                 |  |

|----------------------------------------------------------------|-----------------|--|

| Calculation mode                                               | User Entered Tj |  |

| Junction Temperature Tj (°C)                                   | 25.00           |  |

| Theta JA                                                       |                 |  |

| Effective $\Theta_{JA}$ (°C/W )                                |                 |  |

| Heat Sink                                                      |                 |  |

| Air Flow                                                       |                 |  |

| Custom ⊖ <sub>SA</sub> (°C/W)                                  |                 |  |

| Board Thermal Model                                            |                 |  |

|                                                                |                 |  |

| Thermal data is not yet available for the selected combination |                 |  |

#### **Power Summary**

|                             | -                   |     |       |

|-----------------------------|---------------------|-----|-------|

|                             | Summar              | /   |       |

| Total Power (W)             |                     |     | 1.279 |

| → Device Stat               | → Device Static (W) |     |       |

| Core Dynamic (W)            |                     |     | 0.938 |

|                             |                     |     | 0.288 |

| Transceiver (W)             |                     |     | 0.000 |

| Junction Temperature Tj(°C) |                     |     | 25.00 |

| Effective Theta JA(°C/W)    |                     | N/A |       |

| Thormal Margin              | Maximum Ta(°C)      | N/A |       |

| Thermal Margin              | Maximum Power (W)   | N/A |       |

| Power Breakdown   |            |     |           |  |

|-------------------|------------|-----|-----------|--|

| Resource          |            | %   | Power (W) |  |

| Core Static       |            | 3%  | 0.041     |  |

| Other Rail Static |            | 1%  | 0.013     |  |

| Core Dynamic      | Clock      | 22% | 0.277     |  |

|                   | Logic      | 37% | 0.477     |  |

|                   | Math Block | 11% | 0.143     |  |

|                   | RAMs       | 2%  | 0.029     |  |

|                   | PLL        | 1%  | 0.012     |  |

|                   | DLL        | 0%  | 0.000     |  |

|                   | Crypto     | 0%  | 0.000     |  |

| I/O               | Switching  | 13% | 0.173     |  |

|                   | DC         | 9%  | 0.115     |  |

| Transceiver       |            | 0%  | 0.000     |  |

# What is Available Today

## SDK in GitHub

- Tools

- Model Optimization

- Calibration

- Simulator

- Tutorials

- Documentation

- VectorBlox Website

- Hardware

- Example Projects

| 양 master → 양 1 branch ⓒ 1 tag          |                             | Go to file                    |

|----------------------------------------|-----------------------------|-------------------------------|

| Joel Vandergriendt update for 1 channe | el inputs                   | 23dfc0d yesterday 🕚 4 commits |

| ocs docs                               | Interm Update to V1.0.0     | 9 days ago                    |

| drivers/vectorblox                     | update for 1 channel inputs | yesterday                     |

| example                                | update for 1 channel inputs | yesterday                     |

| 🖿 fw                                   | update for 1 channel inputs | yesterday                     |

| 📄 lib                                  | update for 1 channel inputs | yesterday                     |

| python                                 | update for 1 channel inputs | yesterday                     |

| 📄 tutorials                            | update for 1 channel inputs | yesterday                     |

| 🗅 .gitattributes                       | initial commit              | 3 months ago                  |

| README.md                              | Interm Update to V1.0.0     | 9 days ago                    |

| install_dependencies.sh                | initial commit              | 3 months ago                  |

| 🗅 install_venv.sh                      | Interm Update to V1.0.0     | 9 days ago                    |

| C requirements.txt                     | initial commit              | 3 months ago                  |

| Setup_vars.sh                          | initial commit              | 3 months ago                  |

https://github.com/Microchip-Vectorblox/VectorBlox-SDK http://www.microchip.com/fpga\_VectorBlox

# Thank you!

#### ©2020 Edge AI and Vision Alliance Confidential

#### The Alliance enables edge AI and vision technology providers to grow their businesses through leads, partnerships, and insights

Mission: To inspire and empower engineers to design products that perceive and understand.

The Alliance provides low-cost, high-quality technical educational

For membership, email us: membership@edge-ai-vision.com

solutions providers

The Edge AI and Vision Alliance (<u>www.edge-ai-vision.com</u>) is a partnership

of >100 leading edge AI and vision technology and services suppliers, and

## **Empowering Product Creators to** Harness Edge AI and Vision

Register for updates at www.edge-ai-vision.com

resources for product developers

edge ai + vision ALLIANCE"

## Join us at the Embedded Vision Summit May 25-28, 2021—Online

The only industry event focused on practical techniques and technologies for system and application creators

- "Awesome! I was very inspired!"

- "Fantastic. Learned a lot and met great people."

- "Wonderful speakers and informative exhibits!"

#### **Embedded Vision Summit 2021 highlights:**

+ vision ALLIA

igineers to design systems that **perceive + understand**

- Inspiring keynotes by leading innovators

- High-quality, practical technical, business and product talks

- Exciting **demos**, **tutorials** and **expert bars** of the latest applications and technologies

### Visit <u>www.EmbeddedVisionSummit.com</u> to learn more and register (use promo code EARLYBIRD21 by 4/16 to receive your 15%-off Early Bird Discount!)

embedded

Summit

MAY 25-28

VIS