The Importance of Memory for Breaking the Edge AI Performance Bottleneck

**Wil Florentino**

Sr. Segment Marketing Manager Micron Technology

## **Edge AI reveals memory as the bottleneck**

Model inference

Pre-processing overhead

Communication overhead

time

**Trend toward memory-bound applications**

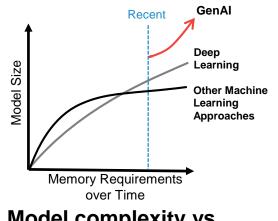

# Model complexity vs. memory bandwidth

- Transformer size growth 410x / 2 years

- AI HW memory bandwidth 2x / 2 years<sup>1</sup>

# Pre-processing latency in AI execution

Data pre-preprocessing overhead<sup>2</sup> impacts latency

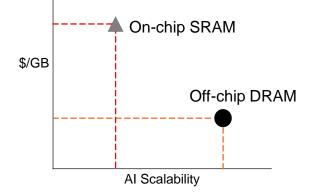

\$/GB vs. scalability

- SRAM: \$5,000/GB

- DRAM: \$50/GB3

Al and memory wall," Medium, 2021 2 "Rapid Data Pre-Processing with NVIDIA DALI" NVIDIA Technical Blog, 2021 3 "SRAM vs. DRAM: Difference between SRAM & DRAM explained," Enterprise Storage Forum, 2023

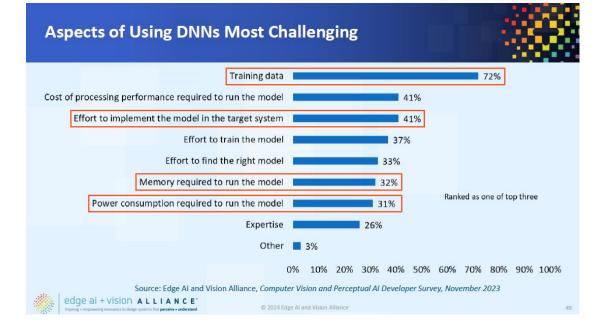

## DNN challenges relate back to memory and storage

Edge AI and Vision Alliance report on DNN implementation challenges

- Training data trade-offs between cost of storage on-premise vs. cloud

- Complexity of on-device implementation in target

- Type of and memory performance influence the efficiency of running the model

- Power consumption

embedded

SUMMIT

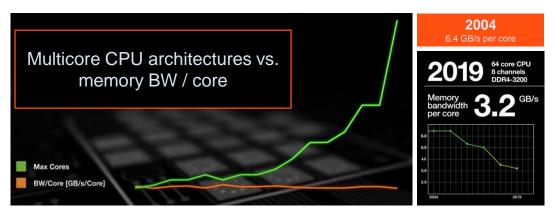

### DRAM memory bandwidth per core has been declining

- CPU core counts are increasing at a rate that minimizes available memory bandwidth per core

- New memory technologies are required to meet next-generation bandwidth-per-core requirements in multi-core CPUs

- Edge AI inference compute requires additional memory consideration

## The many levers of a memory device

Complex design considerations for memory improve performance and lower costs

### Configuration

- Density per die

- Die per package

- I/O width

- Bank groups

- Technology node

### Performance

- Speed/pin

- Number of channels

- Prefetch size

- Burst length

- Read latency

### Operational

- On-die Error Correction

- Thermal profile

- Refresh management

- Power reduction modes

- Active vs. standby power (picojoule/bit)

### **Application focus**

- Functional safety

- Reliability/Availability/Serviceability

- Extended temperature

- Validation and testing

- Product lifecycle

- Industrial rated

- Auto validated

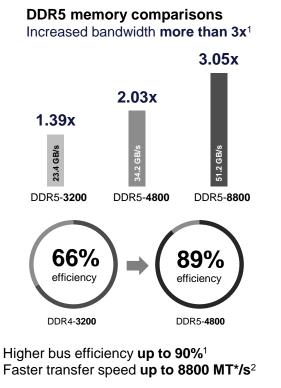

## DDR5 for data-intensive training workloads

## capability

- Burst length

- Bank groups

- Banks

# Improved overall workload performance<sup>3</sup>

**Cloud** Virtualization 40%

|  | _ |

|--|---|

Data center Business apps 45%

**High-performance computing** HPC modeling >200%

6

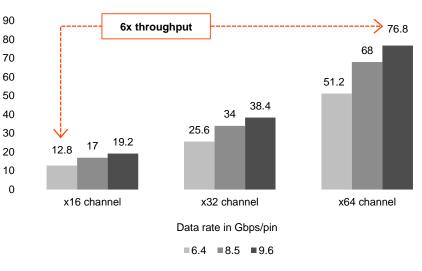

### **Compute bandwidth requirements by edge solution**

AI TOPs\* vs. number of LPDDR4 devices scenarios

**x**16 **x**32 **x**64

|                                                                                  | Sensor edge<br>IoT sensors and ultra low power<br>devices (TinyML) | Device edge<br>Cameras, machines and<br>industrial/SFF PC/server | <b>Network edge</b><br>Industrial PC/server, network<br>equipment, NVR/VMS appliances | Compute edge<br>Server/NVR/VMS<br>appliances |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------|

| Power                                                                            | <1W                                                                | 2W <= 15W                                                        | 15W <=75W                                                                             | 15W <= 75W+                                  |

| SoC/ASIC IO width (typical)                                                      | x16                                                                | x32                                                              | x64                                                                                   | x128                                         |

| DLA INT 8 TOPS                                                                   | <4                                                                 | 4–20                                                             | 20–50                                                                                 | 50–100                                       |

| Est. bandwidth to full<br>utilization of accelerator<br>[saturate accelerator**] | 18 GB/s                                                            | 90 GB/s                                                          | 225 GB/s                                                                              | 451 GB/s                                     |

| BW of LP4 @ 4.2Gbps/pin<br>IO per device (x16/x32/x64)                           | 8 GB/s •                                                           | 17 GB/s •                                                        | 33 GB/s •                                                                             | 33 GB/s •                                    |

| Number of LP4<br>packaged devices                                                | 3                                                                  | 6                                                                | 7                                                                                     | 14!                                          |

<sup>1</sup> \*relative reference models only, actuals will vary.<sup>2</sup> \*\*Device Level Accelerator bandwidth assumed roofline modeling (Resnet 50) <sup>3</sup> "V. Sze, Y. -H. Chen, T. -J. Yang and J. S. Emer, "How to Evaluate Deep Neural Network Processors: TOPS/W (Alone) Considered Harmful," in IEEE Solid-State Circuits Magazine, vol. 12, no. 3, pp. 28-41"

© 2024 Micron Technology

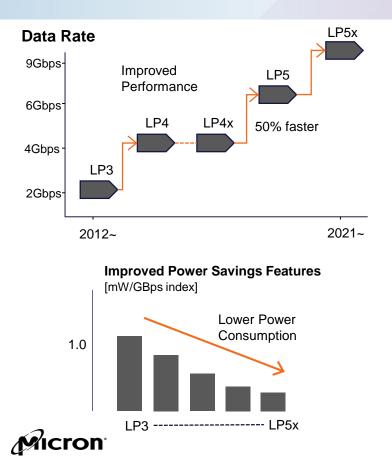

## LPDDR5 offers a leap in performance and possibilities

LPDDR5X bandwidth at different channel and pin speed

- Reduces number of components to get to same bandwidth

- Improved architecture

- Lower power [pj/bit]

GB/s

embedded

SUMMIT

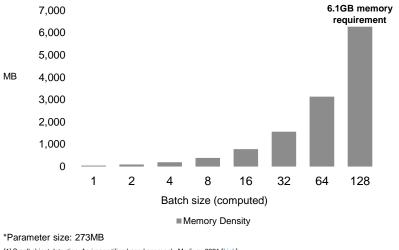

## Memory footprint as a function of batch size

Tiling for small object detection in high-resolution vision

Batch size impacts the memory footprint

Memory for inference YOLOv8x across\* batch sizes

Small object detection: An image tiling based approach, Medium, 2021 [Link]

S. Ngvuyen, et al., "Dynamic tiling: A model-agnostic, adaptive, scalable, and inference-data-centric approach for efficient and accurate small object detection," arXiv:2309.11069v1, 2023

F. Akyon, et al., "The power of tiling for small object detection," VPR, 2019

Training vs. inference – Memory consumption by neural networks [Link]

GitHub: TorchInfo [Link]

GitHub: TorchInfo [Link]

TorchInfo [Link]

Meta AI-generated image (Imagine Platform)

Tiling high-resolution images

Stacked inputs

Example: Batch size: 9 x N

© 2024 Micron Technology

Higher batch size improves results

Convolutional model

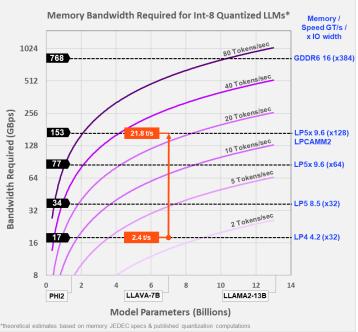

### Why memory is important for generative language

- Bandwidth is critical to quality of service ٠

- Tokens/sec is highly correlated with DRAM bandwidth LLAVA 7B with 8-bit guantization\* ~5 seconds

### LP4 4.2 (x32): 17 GB/s

The image shows a person ironing clothes on a

\* LLAVA (Ilava-vl.github.io) | Assume 1 token/word | Excluding time to first token

### LP5X 9.6 (x128): 153 GB/s

The image depicts an unusual scene where a man is ironing clothes on an ironing board placed on the back of a moving vehicle, specifically a yellow SUV. This is not a typical activity one would expect to see on a city street, as ironing is usually done indoors in a stationary position to ensure safety and to prevent accidents. The man's actions are not only unconventional but also potentially dangerous due to the risk of falling or being hit by other vehicles or pedestrians. Additionally, the presence of a taxicab in the background adds to the urban environment, which makes the scene even more out of the ordinary.

<sup>1</sup> Assumes GGML Quantization: ggml.ai, <sup>2</sup> Kim, Sehoon, et al. "Full stack optimization of transformer inference: a survey." arXiv preprint arXiv:2302.14017 (2023)

10

embedded

SUMMIT

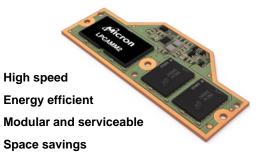

### LPCAMM2 for Al-equipped systems

### Performance

- LPDDR5x speed of up to 9.6Gbps

- Full 128-bit, dual-channel, low-power modular memory solution

### Modularity

- Flexibility to **upgrade system memory** capacity

- Single PCB for all memory configurations

### **Power efficiency**

- Consumes 57%-61%<sup>1</sup> less active power and up to 80%<sup>1</sup> less system standby power compared to DDR5 SODIMM

- Thermal efficiency, fanless computers

### Form factor

- Up to 64%<sup>2</sup> space savings

- Space savings for industrial PCs, embedded single-board computers, AIoT systems

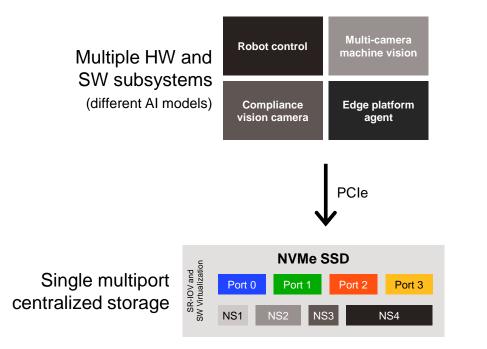

## **Multiport SSD as centralized storage**

Supporting multiple subsystems in a single storage device

### 4150AT product highlights

- **Configurable multiport** (single, dual, triple and quad)

- **SR-IOV** allowing for shared and private namespaces

- Design flexibility to match system usage models with TLC, SLC and HE-SLC endurance modes

- Up to 600K read and 100K write IOPS performance

- -40 C to 115 C Tc operating temperature range

- Fast boot with TTR <100ms</li>

Legend: SR-IOV = single root I/O virtualization, NS = namespace, PF = physical function, VF = virtual function, Tc = case temperature, TTR = time to ready, TLC = triple-level cell, SLC = single-level cell, HE-SLC = high endurance SLC, IOPS = input/output operations per second

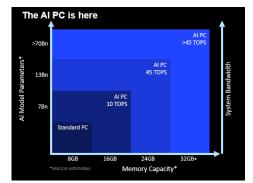

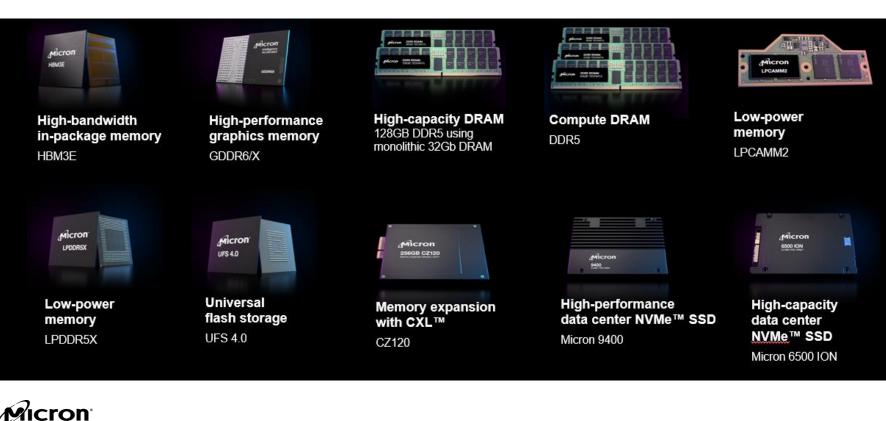

### Micron AI memory and storage portfolio

Leadership products to enable AI workloads

### Summary

### Micron memory enables all forms of AI embedded solutions

Al at the edge (outside the data center) reveals memory as a bottleneck

- · Disproportionate growth between transformer size vs. memory bandwidth

- Data pre-preprocessing overhead impacts latency

- · On-chip SRAM is cost prohibitive vs. external DRAM

### Memory technology influences AI model execution performance

- Edge AI devices TOPS showcase memory bandwidth gap

- · Tiling activation requires in-line memory density resources

- In generative language, bandwidth is required for quality of service

# Leading memory technologies offer the best mix of solutions for edge AI applications

- DDR5 for AI training workloads

- LPDDR4 and LPDDR5 for neural network compute

- LPCAMM2 to leverage LPDDR5X performance with DIMM modularity

- Multiport SSD to support different AI models and compute in a single storage

Smart factory and robotics

Industrial AR/VR Sma

Smart grid and clean energy

Al-enabled video security and analytics

communication

(LEO)

Drones and industrial transport

### Visit us at Booth #105

© 2024 Micron Technology

# **Thank You**

© 2024 Micron Technology