This article was originally published at Mentor's website. It is reprinted here with the permission of Mentor.

In the world-class setting of France’s Sophia Antipolis science park, the BOSCH® Visiontec team innovates assisted and autonomous driving technology. This team develops state-of-the-art IP and ICs containing high-performance processors that implement algorithms to recognize images from cameras in automobiles. They were tasked to create several brand-new designs that implemented mathematically-intense algorithms in less than a year. The specifications of these designs were dynamic and changed throughout the design cycle. There was no way that the team could manually code RTL and verify these designs in this ever-changing environment. So, they decided to move up to the C++ level and employ the Catapult® High-Level Synthesis (HLS) Platform and PowerPro® solutions from Mentor, a Siemens Business. The Catapult HLS Platform allows the team to use C++ to describe functional intent and generate production-quality RTL.

Writing and Verifying the Code

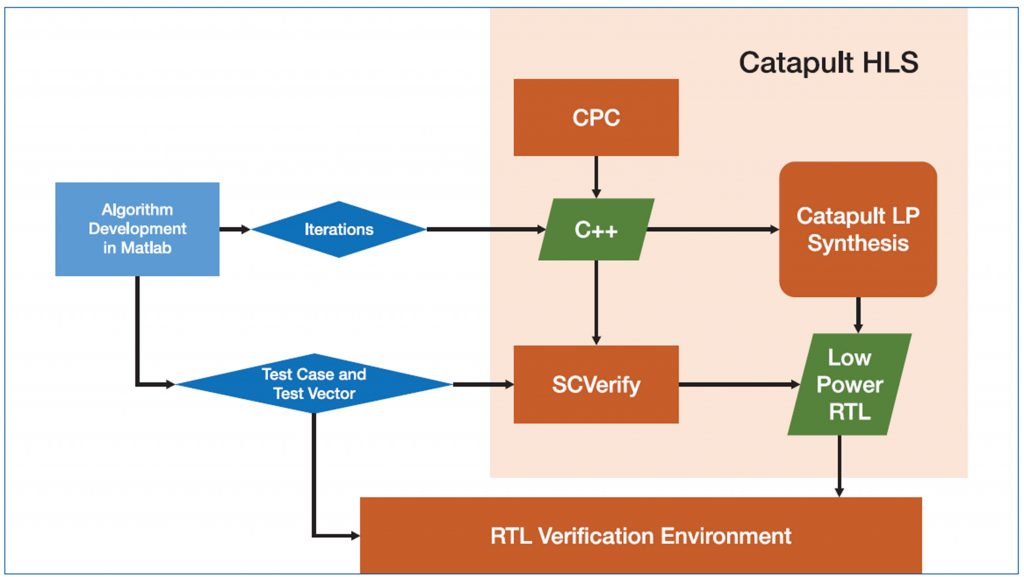

The design and verification flow (Figure 1) begins by writing synthesizable C++ inspired from a Matlab model and from the specification. While writing C++ code, the team ensures that it remains in the defined hardware architecture. For example, the design is partitioned into hierarchical blocks. Writing synthesizable C++ code based on the defined hardware architecture in the beginning of the flow, avoids multiple iterations during synthesis in order to meet performances goals. The team performs extensive verification in the C++ domain, including bit-accurate checks against the reference Matlab models.

All of the designs are new and rich in complex mathematical functions, either trigonometric, scalar, vector or even matrix multiplication and normalization. The team utilizes these functions in multiple designs, so they create parameterized functions to avoid writing the same functions multiple times for different designs. This technique helped save time and to meet precision goals when bit-width changes occurred during the algorithm evolution. Writing these functions in C++ is much easier than writing them in RTL. Catapult can automatically meet timing for these functions as compared to RTL where designers need to ensure timing of these functions after RTL synthesis.

Figure 1: The design and verification flow.

Managing Change

All the algorithms kept evolving during the development stage. So, it was necessary to quickly adopt these changes while generating RTL. With Catapult, the team handles these changes by simply changing constraints in the tool and re-running it to see what the resulting design looks like. This allows them to validate the algorithms and to see the effect on area and performance due to the changes. This is a key differentiator from traditional RTL design where any change in algorithm requires code changes and a lot of subsequent verification. For example, the clock frequency was modified and Catapult synthesized the C++ code to meet post-synthesis timing specifications without any other modifications.

Automating the Verification Flow

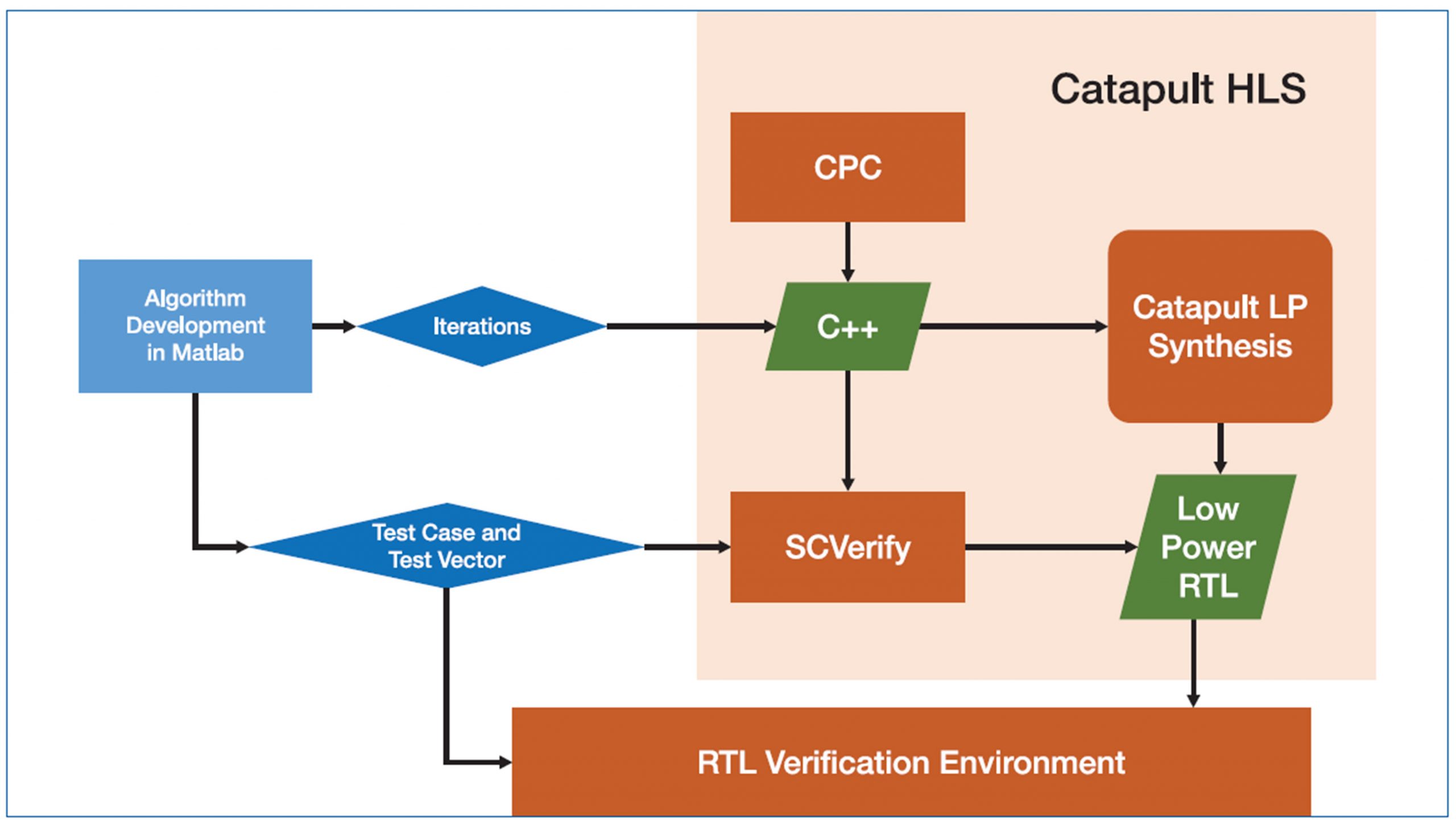

Using the verification flow in Catapult (Figure 2), the team automatically generates the infrastructure for verifying the functionality of the HLS-generated RTL against the original source code and they reuse the original C++ testbench.

Figure 2: The verification flow.

When Catapult compiles C++ design files, it also generates scripts that drive the simulator for debugging and verifying the design. This provides a big advantage to the team for verifying the RTL because with a push of a button it uses the same testbench written to verify C++ code to verify RTL code without writing a RTL testbench. This flow saves considerable verification time compared to a manual flow.

Managing Power

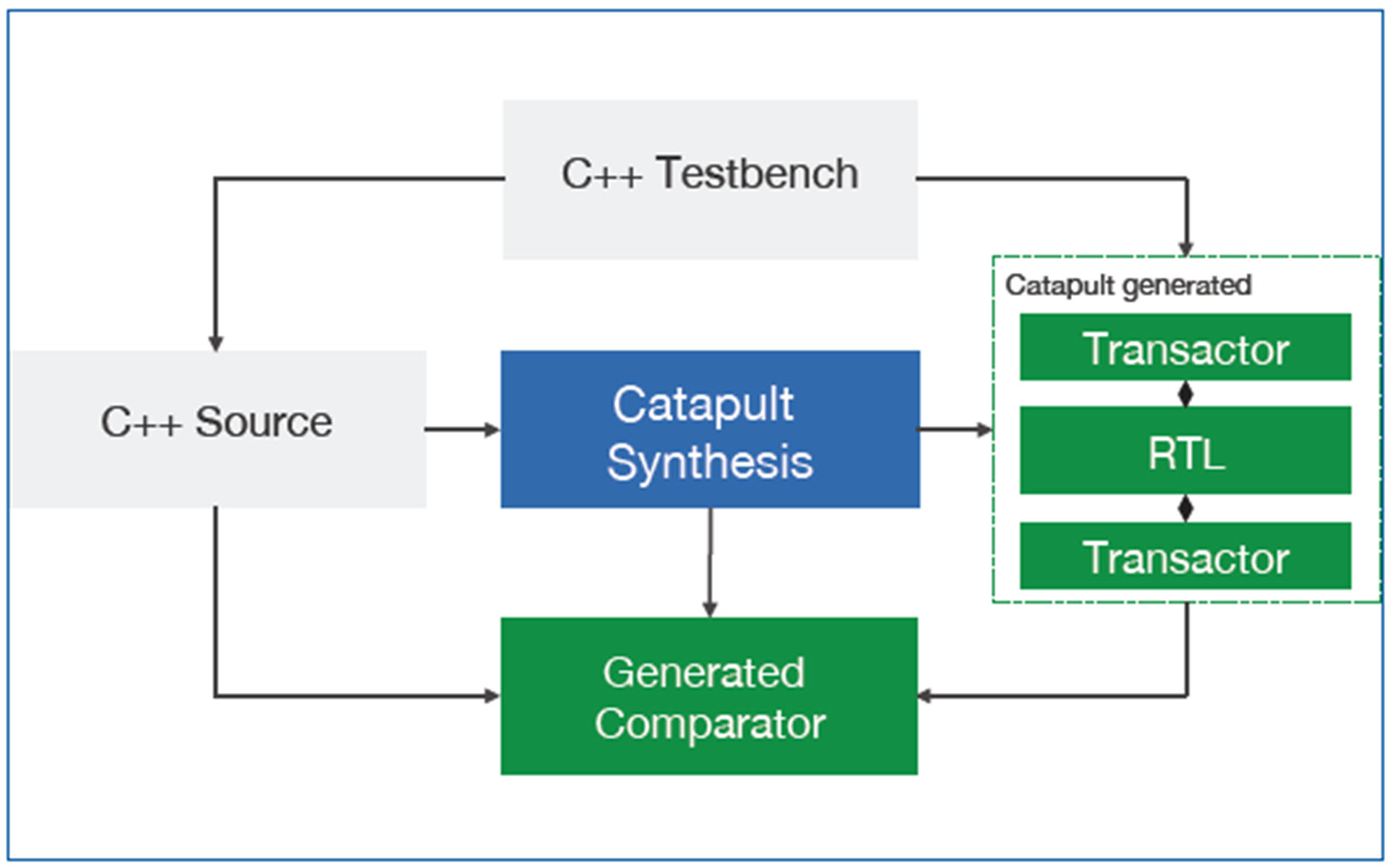

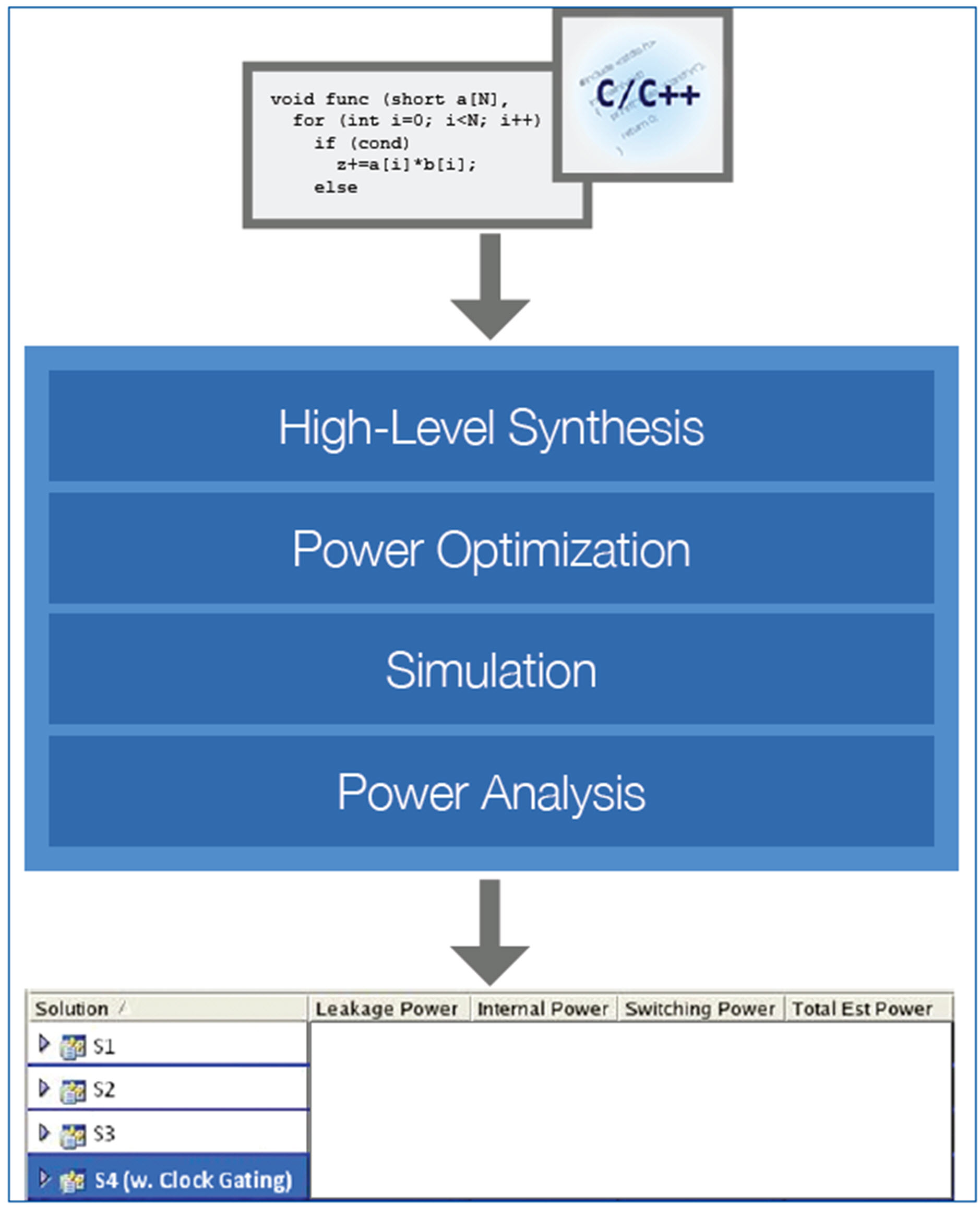

Using the Catapult low-power flow (Figure 3), the team takes advantage of the PowerPro technology to optimize for power. Using stability and observability clock gating, the tool generates power-optimized RTL with minimum guidance. It also uses the same testbench used in the verification flow to capture switching activities in the Switching Activity Interchange Format (SAIF) or Fast Signal DataBase (FSDB) format. The team does not need to write a separate testbench or create an environment for capturing switching activities. In one design, the team saw a 33% power savings using the low-power flow.

Figure 3: The PowerPro flow.

Results

By adopting the Catapult C++ HLS flow with power analysis and optimization, the BOSCH Visiontec team was able to successfully deliver the new designs ahead of schedule in seven months even though the specifications evolved over the design cycle. The quality of results was not only maintained but improved by using Catapult’s micro-architectural exploration, which enabled the team to quickly produce higher quality designs through continuous refinement. Without using the Catapult flow, it would have been impossible to complete the project on time and to specifications.

To learn more about the BOSCH Visiontec success, read the whitepaper here.

By Vishal Sinha

Consultant Application Engineer, Mentor, a Siemens Business