Tensilica Vision P6 DSP increases performance and power efficiency compared to CPUs for vision and AI applications

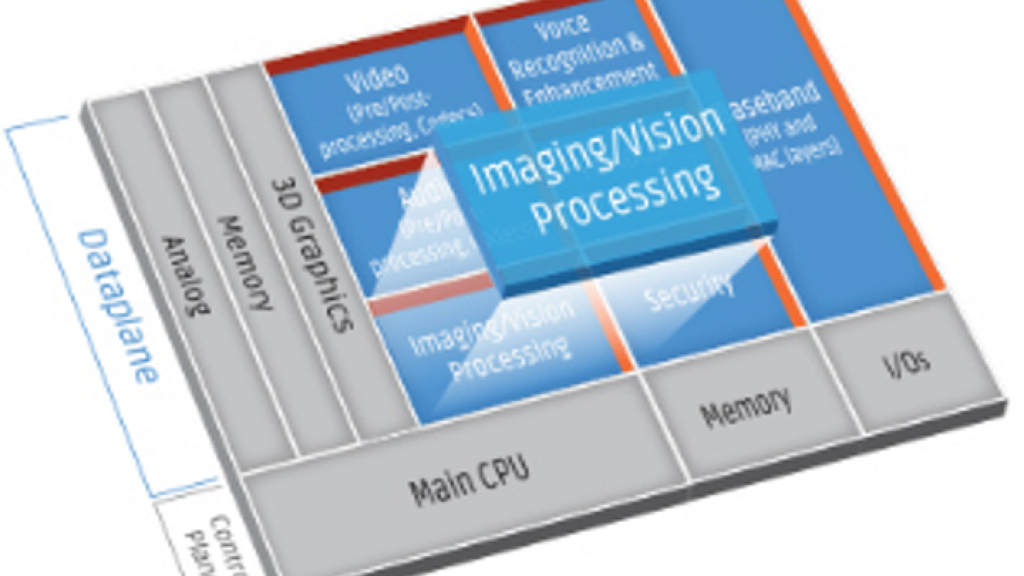

SAN JOSE, Calif., June 13, 2019—Cadence Design Systems, Inc. (NASDAQ: CDNS) announced today that Toshiba has implemented the Cadence® Tensilica® Vision P6 DSPs for its next-generation automotive SoC to meet functional safety requirements. The Vision P6 DSP provides high compute throughput with low power consumption, small core area and a strong partner ecosystem, and is certified to meet functional safety requirements, making it the ideal choice for automotive applications. Offering up to 3.8X more power efficiency than CPUs alone and 1024 giga-operations (GOPS) of processing power, the Vision P6 DSP serves as a powerful offload engine, efficiently processing vision and AI workloads to meet the demands for accurate detection and identification of objects.

For more information on the Tensilica Vision P6 DSP, please visit www.cadence.com/go/visionp6toshiba.

Toshiba has integrated the Cadence Xtensa® Imaging Library (Xi-Lib) into its software development kit (SDK), enabling its customers to easily access the Vision P6 DSP to execute custom algorithms, further strengthening its SDK offering. Using the Xi-Lib allowed Toshiba to easily port their existing vision algorithms to run on the DSP, reducing development time and effort. In addition, the Vision P6 DSP core, development tools and libraries are all designed to enable SoC vendors to achieve ISO 26262 automotive safety integrity level D (ASIL D) certification.

“The Cadence Tensilica Vision P6 DSP provides outstanding performance as the image recognition processor in our next-generation ADAS chip. This DSP enabled us to execute complex algorithms for accurate detection and identification of a wide range of objects while consuming very low power, which is crucial for today’s automotive applications,” said Nobuaki Otsuka, Technology Executive at Toshiba Electronic Device & Storage Corporation. “The integration of four Vision P6 DSPs in our design gives an immense amount of performance throughput and headroom to meet current and future requirements for many of our advanced driver assistance systems and autonomous driving functions.”

“By leveraging the optimized instruction set of the Vision P6 DSP, Toshiba can execute several driver-assistance functions simultaneously on one chip and in real time,” said Pulin Desai, director of product marketing for the Tensilica Vision DSP product line, IP Group at Cadence. “The Vision P6 DSP development tools and libraries are also designed for ISO 26262 ASIL D certification, which is critical when developing automotive-grade solutions.”

The Vision P6 DSP also supports AI applications developed in the Caffe and TensorFlow frameworks through the Tensilica Neural Network Compiler (XNNC). The compiler maps neural networks (NNs) into executable and highly optimized high-performance code for the Vision P6 DSP, leveraging a comprehensive set of optimized neural network library functions from the Tensilica NN library. The Vision P6 DSP also supports the Android Neural Network (ANN) API for on-device AI acceleration in Android-powered devices. The Vision P6 DSP has been integrated in top-tier mobile phone application processors, surveillance camera processors and AR/VR processors.

About Cadence

Cadence enables electronic systems and semiconductor companies to create the innovative end products that are transforming the way people live, work and play. Cadence’s software, hardware and semiconductor IP are used by customers to deliver products to market faster. The company’s Intelligent System Design strategy helps customers develop differentiated products—from chips to boards to systems—in mobile, consumer, cloud data center, automotive, aerospace, IoT, industrial and other market segments. Cadence is listed as one of Fortune Magazine's 100 Best Companies to Work For. Learn more at cadence.com.