This blog post was originally published at Arm’s website. It is reprinted here with the permission of Arm.

AMBA is being extended to the chiplets market with the new CHI C2C specification.

As Arm’s EVP and Chief Architect Richard Grisenthwaite said in this blog, Arm is collaborating across the ecosystem on standards to enable a thriving chiplets market. A significant part of this ecosystem collaboration is the work on the brand-new AMBA CHI C2C specification for chiplets.

The origins of AMBA

For nearly 30 years AMBA™ has been the foundational open standard for the fabless semiconductor industry. Essentially, it is a set of architecture specifications that defines interfaces and protocols to connect various components in the chip together. So, if a CPU wants to load or store data in memory, it uses AMBA to communicate to a memory controller. In the age of AI, if a particular AI-based workload requires acceleration and is split across various processing elements, like the CPU, GPU or NPU, then each one will exchange data and synchronization information over the AMBA interfaces.

AMBA addresses a wide variety of power, performance and area requirements for silicon. This provides the industry with access to a comprehensive set of compatible and proven solutions that can be re-used and integrated easily. Ultimately, this lowers risk, lowers cost and provides a quicker time to market.

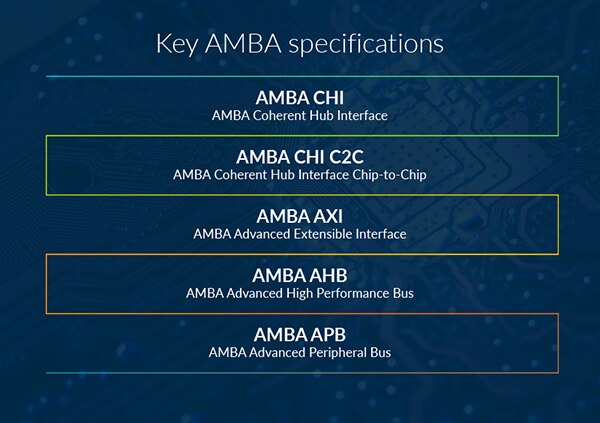

Making AMBA a success has involved extensive collaboration across a diverse range of ecosystem partners. This has led to an ongoing evolution of AMBA from simple and low bandwidth protocols through AHB and APB, to AXI for higher performance. More recently, the CHI protocol was introduced for extremely performance systems, as well as systems with a vast network of components, processors, and elements. The end result is billions of devices worldwide all implementing these AMBA specifications.

Now, we are extending AMBA to the chiplets market with CHI C2C. This represents the next evolution of AMBA and a significant step-change for the specification to be used even more widely by the industry. CHI C2C is important for the chiplets market because putting the right foundational standards in place now will enable chiplets to be used across a wide variety of computing systems without the risk of fragmentation.

Why AMBA CHI for chiplets?

The AMBA CHI C2C specification leverages the existing single chip CHI protocol and defines how it is packetized, which enables it to be transported chiplet-to-chiplet. As AMBA already connects the different components in a single chip, the natural progression through the CHI C2C specification is extending this connectivity across multiple chiplets.

Through developing CHI C2C, we have leveraged many features from the existing on-chip AMBA CHI specification. CHI C2C inherits the existing on-chip protocol to avoid incompatibilities. It allows the same architecture features from the existing AMBA specifications to be used across chiplets, like realm management for confidential compute. There is also no complex packing or unpacking with CHI C2C, which minimizes latency. As with AMBA for existing on-chip designs, we expect CHI C2C to be used across very high-performance systems that have a vast number of processors and components

CHI C2C addresses the growing demands for custom silicon, ideal for our partners looking to integrate computing systems with chiplets to design custom silicon. With different chiplet components coming from various vendors, CHI C2C ensures maximum interoperability for chiplets through a single, unified interface. These include chiplet designs for AI acceleration.

To address the interoperability challenge and enable breakthroughs in AI and accelerated computing, for several years Arm and NVIDIA worked closely together to define and lay the foundation for CHI C2C, so Arm-based systems-on-chip (SoCs) can coherently and securely connect to accelerators.

As CHI C2C follows a layered approach that offers a clean separation of layers, it can use third-party and industry standards, like the Universal Chiplet Interconnect Express (UCIe) standard. UCIe is particularly important to CHI C2C, as it helps to standardize die-to-die connectivity in multi-die systems and also streamlines interoperability between dies on different process technologies from different suppliers. In fact, CHI C2C is completely complementary to UCIe, as it can be transported over UCIe through its streaming interface.

Finally, we have committed to delivering an open AMBA AXI C2C specification that can be adopted by silicon vendors who have been using AMBA AXI in their existing single on-chip designs. This is critical to enabling alignment with CHI C2C and also for future interoperability in chiplets.

True ecosystem collaboration

The release of the AMBA CHI C2C specification is the result of extensive collaborations with a diverse set of industry partners, including Arteris, Cadence, Fujitsu, Intel Foundry Services, NVIDIA, Rambus, Sanechips, Siemens EDA, SiPearl and Synopsys. It is this thriving ecosystem collaboration that has brought AMBA to life and made it a success.

Here is what some of the partners involved in the development and release of the CHI C2C specification have to say:

“The release of the first public CHI C2C specification marks a significant step towards an open chiplet ecosystem and contributes to improvements in interoperability. We are pleased to partner with Arm on early AMBA developments as it will impact future versions of our high-bandwidth, low-latency network-on-chip interconnect IP technology including Ncore and FlexNoC. We look forward to further cooperation across the emerging chiplet ecosystem.”

Laurent Moll, COO of Arteris

“With its disaggregated solutions in the form of chiplets, droplets, dielets, tiles and such, the More-than-Moore era presents significant opportunities and technology challenges for both designers and implementers. The need for standardized interfaces is paramount to facilitate communication between chiplets from a multitude of providers and to avoid building a tower of Babel. Cadence has a history of close collaboration with Arm on AMBA standards, and we’re pleased to build upon our partnership and bring the new AMBA CHI C2C standard to market in our IP and chiplet solutions encompassing flows, reference designs and customer designs. This important new standard will be a key ecosystem enabler and should promote an open chiplet marketplace, which is still in its nascent stage.”

David Glasco, VP of R&D for the Silicon Solutions Group at Cadence

“Fujitsu considers chiplets as essential technology for future processor architectures. We’re already adopters of the open, foundational AMBA specifications, and the latest AMBA CHI C2C specification is a step-change in establishing how to transport data efficiently in low-latency off-chip use cases, such as chiplet-to-chiplet. We’re excited to see how this will enable the chiplet ecosystem.”

Toshio Yoshida, Executive Director, Advanced Technology Development Unit, Fujitsu

“Intel® has long envisioned a “chiplet revolution,” which was the motivation for our introducing the UCIe protocol to the industry in 2022. We are pleased to see the industry’s growth and adoption of UCIe™, advanced packaging technologies, and standards-based protocol mapping. Along with UCIe, the standardization and release of the AMBA CHI C2C specification is a critical building block for the industry’s drive toward chiplet based architectures and we are excited to continue our collaboration with Arm.”

Bob Brennan, IFS, VP, Customer Solutions Engineering, Intel

“The AMBA CHI C2C specification will enable efficient chip-to-chip interconnectivity, allowing the creation of powerful AI systems that support coherency and confidential compute for a wide variety of use cases, from chiplets to off-package connectivity. Our significant work over the past four years to advance this new standard, in collaboration with Arm and other ecosystem partners, will help propel the industry forward and drive breakthroughs in AI and accelerated computing.”

Ashish Karandikar, Vice President of Hardware Engineering, NVIDIA

“Chiplets provide a key architectural solution for the acceleration of computing performance needed by AI and other advanced workloads. As longstanding members of the AMBA ecosystem, we are excited to support the AMBA CHI C2C specification as an important enabling technology for next-generation chiplet designs.”

Neeraj Paliwal, General Manager of Silicon IP, Rambus

“Chiplets will definitely be an effectively solution in the semiconductor industry for next decade to address dramatically cost of high performance SoC with advanced process node. Together, UCIe PHY will be used as the physical layer standard for chiplets interconnect and AMBA CHI C2C will be used as an open standard for the protocol layer for chiplets interconnect to extend on-chip CHI to multi-chiplet interconnect. AMBA CHI C2C ensures Arm architecture features like security, virtualization, etc. extend to multi-chiplet boundary and also lower chiplet-to-chiplet latency without additional protocol transition. AMBA CHI C2C is a fundamental protocol to enable compute chiplets, IO chiplets and accelerator chiplets that are interoperable across the extensive Arm architecture ecosystem.”

Owen Shi, Vice President of Sanechips

“Siemens EDA is pleased to support the development of AMBA, taking AMBA CHI C2C protocol to the growing chiplet ecosystem, which is an area of Siemens’ focus with our Avery Verification IP and Veloce hardware-assisted verification solutions.”

Abhi Kolpekwar, VP and General Manager of Digital Verification Technology at Siemens EDA

“Chiplet-based architecture for compute could be a game-changer for Europe in the era of ubiquitous AI. In this context, one of the main challenges is to guarantee interoperability and composability at pace. The new AMBA CHI C2C specification will be key to achieving this. We’ve been proud to collaborate with Arm and the ecosystem in its development and release.”

Philippe Notton, CEO & Founder of SiPearl

“With the shift to multi-die systems, designers require standard interfaces to maximize chiplet interoperability and minimize latency. Synopsys worked closely with Arm and its ecosystem to develop and optimize the CHI C2C specification. Supported by the complete Synopsys UCIe IP solution, this new chiplet standard will accelerate time-to-market and reduce die-to-die latency for a wide array of high-performance applications using Arm technology. This announcement builds on our longstanding technical engagement with Arm to optimize interoperability, performance, and bandwidth of systems that integrate Arm processors and Synopsys IP.”

John Koeter, Senior Vice President of Marketing and Strategy for IP at Synopsys

The foundation for the next era of silicon

As the semiconductor fabless industry embraces chiplets, it is the right time to extend AMBA from single on-chip to multi-chip. As with AMBA’s development in the past 30 years, we are continuing our heritage of open, extensive ecosystem collaborations to deliver AMBA CHI C2C as the foundation for a new era of silicon.

Arm has a proven track record of assessing new and emerging markets and then delivering system architecture standards at the right time to enable the industry to deploy at scale. We are looking to achieve similar success through CHI C2C in the chiplets market.

The CHI C2C specification follows the existing AMBA licensing model. This means it is freely available, royalty free, architecture neutral, and has broad and perpetual implementation rights. In other words, it is ideal for widespread adoption.

We expect the AMBA CHI C2C specification to be used across various segments and applications, starting with high-performance infrastructure applications and quickly followed by automotive. We look forward to continuing the tremendous collaboration around AMBA CHI C2C, which will enable the semiconductor industry to build innovative chiplet solutions better and faster.

To download the AMBA CHI C2C specification click here.

To learn more about AMBA visit here.

Francisco Socal

Director of Product Management, Architecture and Technology Group, Arm