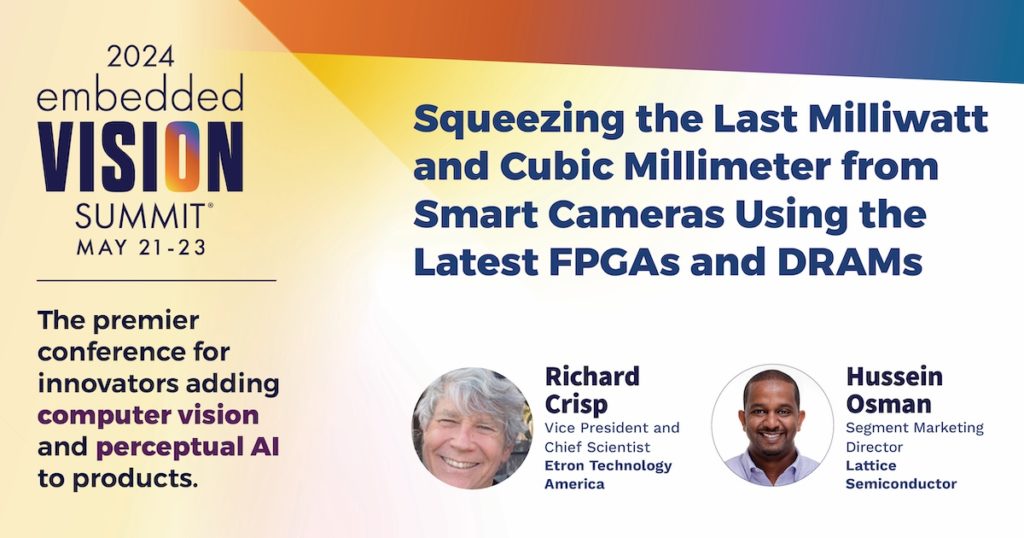

Hussein Osman, Segment Marketing Director at Lattice Semiconductor, and Richard Crisp, Vice President and Chief Scientist at Etron Technology America, co-presents the “Squeezing the Last Milliwatt and Cubic Millimeter from Smart Cameras Using the Latest FPGAs and DRAMs” tutorial at the May 2024 Embedded Vision Summit.

Attaining the lowest power, size and cost for a smart camera requires carefully matching the hardware to the actual application requirements. General-purpose media processors may appear attractive and easy to use, but often include unneeded features which increase system size, weight, power and cost. “Right-sizing” the camera design for the application requirements can save significant power, cost, size and weight.

In this talk, Osman and Crisp show how you can leverage an advanced power-optimized FPGA incorporating a soft RISC-V core combined with a video-bandwidth, low-pin-count DRAM to cut power consumption roughly in half for endpoint smart cameras used in automotive, industrial and other applications. They examine techniques for reducing power, cost and size including system architecture, memory architecture, packaging, and signaling and termination schemes. They also explore techniques for enhancing system reliability.

See here for a PDF of the slides.