High-performance computing, 6G communication, autonomous vehicle chips, and consumer electronics are all key markets that benefit from advancing semiconductor packaging. IDTechEx’s report, “Advanced Semiconductor Packaging 2024-2034: Forecasts, Technologies, Applications“, goes into detail about emerging technologies, including 2.5D and 3D packaging.

The level up

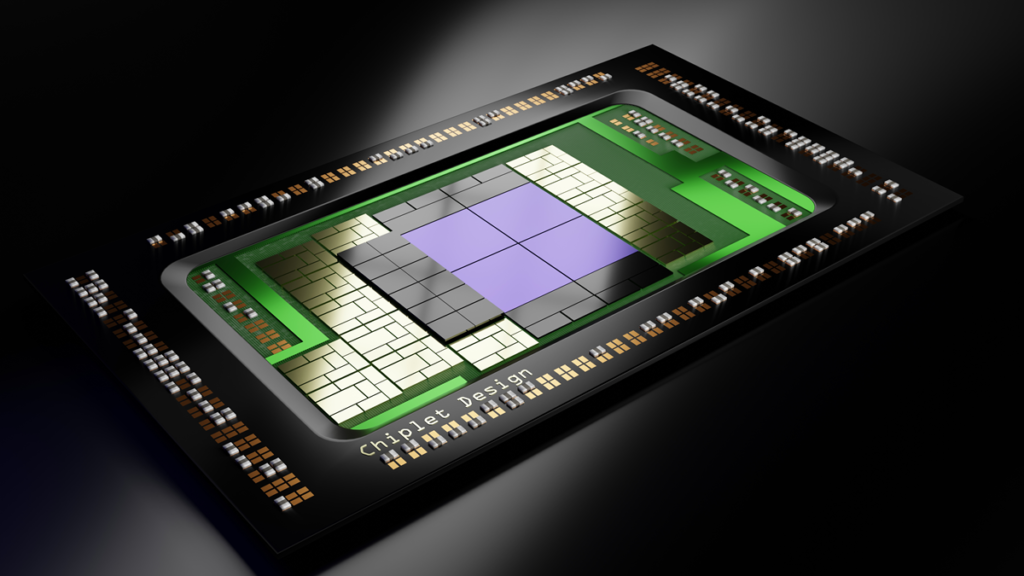

While 1D and 2D semiconductor technologies continue to dominate many applications, the future of advancement lies in 2.5D and 3D packaging, which leverage wafer-level integration. The miniaturization of components means the possibility of greater interconnection densities, which are suited to a wider variety of applications.

Power efficiency, high performance to enable higher bandwidths, increased demand for larger packaging areas, and cost, are all key factors for players in this market to consider. These competitive qualities undoubtedly lead to more challenges, including the need to keep form factors as small as possible to maintain connection while meeting the demands of product manufacturers and keeping costs low.

2.5D packaging

Boosting the performance of computing units can be achieved with larger 2.5D packaging areas, with more space to house computing and memory units together. This can be difficult to achieve on a desired scale for incumbent silicon interposer technologies. This is where a shift is needed from silicon interposers to silicon bridges or other alternatives such as high-density fan-out. IDTechEx explores these in great detail within the “Advanced Semiconductor Packaging 2024-2034: Forecasts, Technologies, Applications” report.

Cost reductions are also necessary going forward to make 2.5D packaging more widely available, as silicon is more expensive than its alternatives. Organic materials could be used for insulation layers in cost-sensitive applications, while glass could also work as a cost-effective substitute.

Performance and device reliability, however, are factors that cannot be overlooked, and chips on a silicon base with surrounding organic materials may not be as effective. Lots of challenges, including warpage management, need to be addressed when packaging components of different materials together, so finding the right materials and manufacturing techniques is important – something IDTechEx explores further within the “Advanced Semiconductor Packaging 2024-2034: Forecasts, Technologies, Applications” report.

3D hybrid bonding

3D packaging brings new structures into play, including the integration of one active die on top of another active die, as well as the aim of decreasing bump pitch distance in the future (the distance between two adjacent balls connecting the die and substrates). This 3D hybrid bonding can be used for applications such as CMOS image sensors, memory (3D NAND Flash and HBM), and logic (chiplets).

However, manufacturing and costs are some of the largest challenges for 3D hybrid bonding. 3D packaging requires a very flat surface to gain good bonding quality between components, and with high-quality tools and materials comes increased costs.

Players that are succeeding in the advanced semiconductor packaging market and offering solutions include TSMC, Intel, and Samsung, with TSMC being the leading player in 3D packaging and the market overall. Bumping pitch and commercial capabilities will play a role in companies’ successes.

New materials and manufacturing processes will continue to be developed to achieve the best performance possible for advanced semiconductor packaging. Improving system bandwidth and power efficiency is predicted to be achieved in the future by increasing I/O routing density and reducing I/O bump size, while cost reductions will continue to be a target for manufacturers and customers.

To find out more about the IDTechEx report “Advanced Semiconductor Packaging 2024-2034: Forecasts, Technologies, Applications”, including downloadable sample pages, please see www.IDTechEx.com/ASP.

For the full portfolio of semiconductor market research available from IDTechEx, please visit www.IDTechEx.com/Research/Semiconductors.

About IDTechEx

IDTechEx provides trusted independent research on emerging technologies and their markets. Since 1999, we have been helping our clients to understand new technologies, their supply chains, market requirements, opportunities and forecasts. For more information, contact [email protected] or visit www.IDTechEx.com.